科研人员研发出互补单晶硅垂直沟道晶体管架构

文章导读

芯片性能瓶颈如何突破?中科院微电子所重磅揭秘:全球首创单片集成互补垂直沟道晶体管(CVFET)架构,性能碾压传统CFET!采用CMOS兼容双侧面工艺,通过创新两步外延技术实现n/p型纳米片自对准堆叠,亚阈值摆幅低至69mV/dec,电流开关比超500万倍。实测反相器在0.8V超低电压下噪声容限提升30%,功耗骤降的同时信号稳定性飞跃。这项登顶IEEE Electron Device Letters的突破,将为3纳米以下芯片制造提供关键路径——读完即知,中国科研如何用"垂直革命"重塑半导体未来!

— 内容由好学术AI分析文章内容生成,仅供参考。

近日,中国科学院微电子研究所研究人员基于自主研发的垂直沟道技术,研发出优于互补场效晶体管架构(CFET)的单片集成互补垂直沟道晶体管结构(CVFET)。

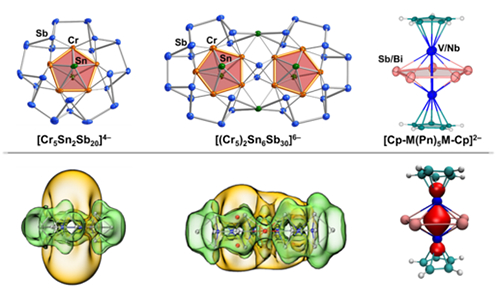

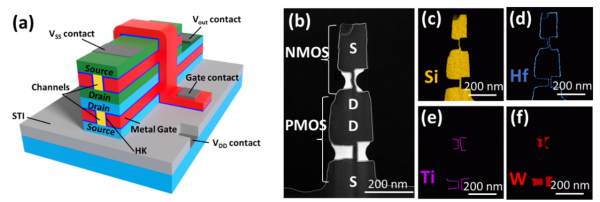

该架构制造工艺采用与CMOS制造工艺兼容的双侧面技术,通过两步外延工艺分别控制纳米片沟道厚度和栅极长度,实现n型和p型纳米片晶体管的上下堆叠和自对准一体集成。CVFET具有如下电学特性:上下层器件亚阈值摆幅分别为69 mV/dec和72 mV/dec,漏致势垒降低分别为12 mV/V和18 mV/V,电流开关比分别为3.1×106和5.4×106。CVFET的CMOS反相器可实现正常的信号相位反转功能,在1.2 V电源电压下,反相器增益为13 V/V;在0.8 V工作电压下,高电平噪声容限和低电平噪声容限分别为0.343 V和0.245 V。

相关研究成果发表在IEEE Electron Device Letters上。研究工作得到国家自然科学基金和中国科学院战略性先导专项(A类)等的支持。

(a) 单片集成CVFET器件架构图; (b)单片集成CVFET器件的TEM截面图和(c-f)EDX元素分布图

© 版权声明

本文由分享者转载或发布,内容仅供学习和交流,版权归原文作者所有。如有侵权,请留言联系更正或删除。

相关文章

暂无评论...