湖南大学段曦东教授团队在二维电子器件电介质领域取得新进展

文章导读

你正准备把二维半导体器件用在下一代超低功耗芯片里,却被一个看不见的“界面魔咒”卡住:高κ电介质要么转移后引入缺陷,要么直接生长又无法在惰性表面铺开,结果是开关效率和功耗始终达不到设计目标。大多数团队还在靠折中方案和复杂工艺把问题掩盖住,实测数据显示界面陷阱和不均匀性是性能天花板的主要源头。湖南大学段曦东团队用范德华外延把问题从根上重新定义——不到两分钟就诱导出定向拼接的单晶Sb2O3薄膜,电介质常数、击穿场强和界面陷阱都达到与器件尺度匹配的水准,60片器件95%成品率、1 V下增益达13的表现更暗示了可量产潜力。文章在Nature Electronics发表,但决定你要不要把这门工艺纳入路线图的那个细节,还藏在他们如何“解耦成核与外延”的工艺里——你准备好看到这一步的真实代价了吗?

— 内容由好学术AI分析文章内容生成,仅供参考。

二维半导体凭借原子级厚度、高迁移率、无悬空键等优异特性,被认为是突破硅基半导体物理极限的核心候选材料之一。实现原子级薄高κ电介质层与二维半导体的高质量无损集成,是二维半导体器件微型化、高性能化的关键,直接决定了器件的开关效率与功耗。当前,多数候选电介质材料需要经过转移过程才能与二维半导体结合,易引入缺陷、破坏界面完整性;传统电介质材料难以在二维半导体的惰性表面实现高质量生长,界面相容性差、缺陷密度高,严重制约了领域发展。

针对这一关键挑战,段曦东教授团队提出了范德华外延生长策略,成功在2D半导体(如p型WSe₂,n型MoS₂)表面实现了单晶Sb₂O₃电介质的定向生长。团队采用两步法工艺解耦成核与外延过程,诱导单向排列的Sb₂O₃晶畴成核、拼接,在不到两分钟的生长时间内制备出均匀性优异的单晶薄膜。

性能测试表明,单层Sb₂O₃介电常数达到6,击穿场强约为11 MV·cm⁻¹,界面陷阱密度低至3.8×10¹⁰ cm⁻²·eV⁻¹。基于单层Sb₂O₃/双层WSe₂异质结构(EOT仅0.4 nm)构建的顶栅场效应晶体管,其亚阈值摆幅低至62 mV·dec⁻¹,开关比高达10⁶,栅漏电流仅为10⁻⁴ A·cm⁻²。此外团队制备的60个顶栅WSe₂晶体管阵列成品率达95%,构建的互补逻辑反相器在1 V电源电压下最大电压增益达13,验证了技术可扩展性。

研究成果以“Epitaxially-grown single-crystalline antimony trioxide dielectrics for two-dimensional electronics”为题发表于Nature Electronics。湖南大学为论文第一单位,段曦东教授、李佳教授、吴瑞霞副教授为论文共同通讯作者,湖南大学化学化工学院博士生张紫媚、半导体学院张正伟教授为论文共同第一作者。

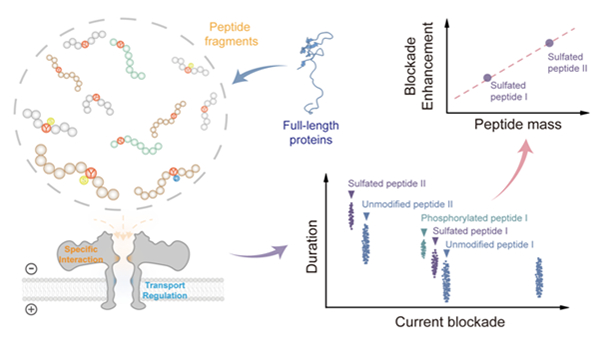

图1 薄层单晶Sb2O3的介电特性。

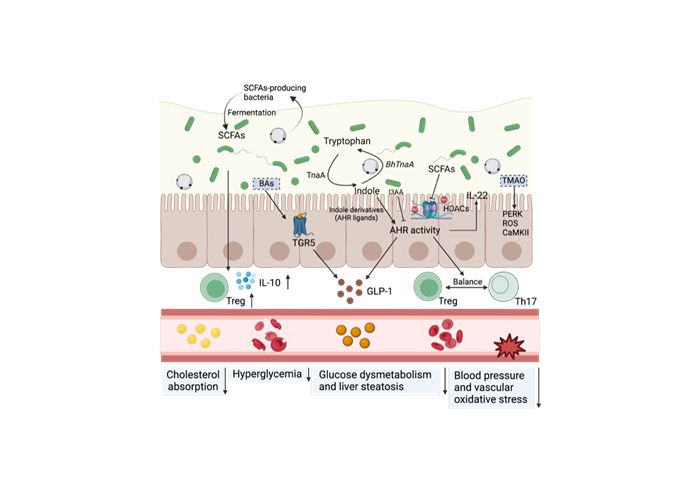

图2 外延生长的1-3层Sb2O3/WSe2顶栅场效应晶体管特性。

来源:化学化工学院

通讯员:陈四海

责任编辑:余楚倩

© 版权声明

本文由分享者转载或发布,内容仅供学习和交流,版权归原文作者所有。如有侵权,请留言联系更正或删除。

95%的成品率真的假的,批量生产有戏?

之前做实验也被界面缺陷坑过,深有体会。

不懂就问,这个成果能用在手机芯片上吗?

这个开关比也太牛了吧!