高性能时钟芯片研究取得进展

文章导读

你是否想过,未来高速通信的“心跳”将由一颗微小芯片精准掌控?面对5.5G乃至6G对时钟抖动的极致要求,传统方案正逼近极限。中科院微电子所与清华大学联手破局,首创双边沿乒乓亚采样锁相环架构,巧妙利用时钟双沿实现等效倍频,一举打破环路带宽、噪声与杂散难以兼顾的设计困局。搭配高效谐波整形技术,芯片在22.4–25.6GHz高频下实现低于18mW功耗与50fs级抖动,抖动—功耗优值达−254dB以下,性能国际领先。这项突破将为下一代高速通信提供核心时钟支撑。

— 内容由好学术AI分析文章内容生成,仅供参考。

5.5G/6G无线通信技术的迭代演进及下一代串行接口向更高传输速率突破,对毫米波本振时钟抖动性能提出了更严苛的要求。亚采样锁相环凭借其高鉴相增益的优势,成为低抖动时钟芯片的主流解决方案,但仍面临挑战。

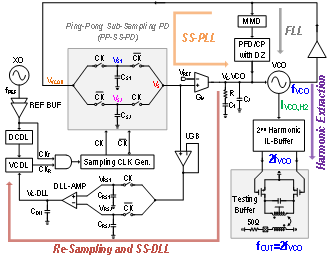

中国科学院微电子研究所与清华大学合作,提出双边沿乒乓亚采样锁相环架构。该架构同时利用参考时钟的上升沿与下降沿,实现了参考频率的等效倍频,解决了传统亚采样锁相环在环路带宽、带内相位噪声与参考杂散之间存在的设计折衷难题。团队还提出高功率与面积效率的注入锁定缓冲器方案,该结构在高效提取振荡器二次谐波的同时能够实现谐波整形,降低了锁相环带外相位噪声。

基于上述两种技术,团队采用65nm CMOS工艺设计了一款K波段锁相环时钟芯片,输出频率覆盖22.4GHz至25.6GHz,整体功耗低于18mW,RMS积分抖动优于50fs,其抖动—功耗优值达到−254dB以下。

相关研究成果在线发表在《IEEE固态电路学报》(IEEE Journal of Solid-State Circuits)上。研究工作得到国家自然科学基金的支持。

乒乓亚采样锁相环电路结构

© 版权声明

本文由分享者转载或发布,内容仅供学习和交流,版权归原文作者所有。如有侵权,请留言联系更正或删除。

期待看到更多国产芯片突破

这个成果发在JSSC上,水平很高啊

科研人员辛苦了,继续加油💪

功耗控制得真不错,才18mW

这种技术突破对5G发展很关键啊

论文链接在哪里?想看详细数据

有懂行的解释下什么是亚采样锁相环吗?

50fs的抖动性能确实很优秀

希望能早日应用到实际产品中

这个研究太厉害了!👍