研究提出基于RISC-V指令集的异构计算系统

文章导读

计算的性能瓶颈和代码适配焦头烂额?中科院软件所重磅突破:无需修改一行源代码,RISC-V指令集竟能实现异构核心间"透明迁移"!其研发的Chimera系统,通过二进制重写技术,将错误恢复频率狂降10000倍,性能开销仅3.2%,更在SPEC测试中性能飙升42.5%。它直击传统系统硬件隔离与运行时开销痛点,一举破解RISC-V生态碎片化困局——性能提升12.5%~33.1%,透明迁移从此不再是梦。前沿技术落地,开发者必看!

— 内容由好学术AI分析文章内容生成,仅供参考。

近日,中国科学院软件研究所研究团队,提出基于RISC-V指令集的ISAX异构计算系统,其通过RISC-V二进制重写技术,无需修改源代码,便可实现异构核心间计算任务的高效透明迁移。该系统有助于解决传统异构计算系统存在的硬件资源隔离和运行时开销过大等性能瓶颈,并为破解RISC-V生态碎片化的软硬件适配难题提供了关键技术支撑。

ISAX(ISA+eXtension)异构计算架构允许不同处理器核心,在共享同一基础指令集的同时,支持不同扩展指令集。此类异构架构的能耗和性能相较同构核心更具优势,却面临异构核心间难以透明迁移问题。

为实现透明迁移,ISAX运行的系统需要对扩展指令进行翻译,并将翻译结果写入二进制文件,从而在运行时根据实际硬件环境自动切换到相应指令序列,在保障高性能的同时实现对用户透明。目前,异构计算系统主要采用编译方法或二进制重写方法,但二者均存在一定局限。

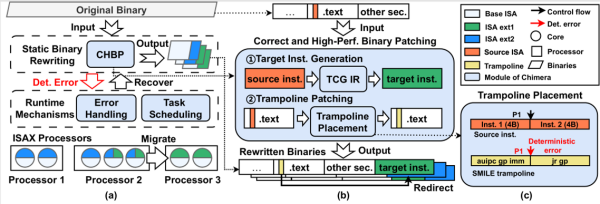

针对上述问题,研究团队设计出基于软硬件协同设计的RISC-V异构计算系统Chimera。该系统基于二进制重写方法,利用RISC-V指令集的编码特性,使可能出现的运行错误具备确定性与可恢复性,并借助轻量级机制实现安全恢复。相比于现有基于二进制重写方法设计的系统,新系统错误恢复机制的触发频率整体降低4个数量级,在无需源代码的情况下,实现了异构RISC-V处理器核心间高效、透明且正确性有保障的任务迁移与调度。

在性能评估中,团队将Chimera与多种现有异构计算系统进行对比实验,包括基于原生编译的MELF、基于二进制重写的Safer及基于运行时调度的FAM。实验表明,在ISAX异构的硬件环境中,Chimera较Safer(不保证正确性)和FAM(不支持透明迁移),分别实现了12.5%和33.1%的性能提升。相较依赖源码的MELF、Safer和FAM的性能开销,Chimera的性能开销仅为3.2%。同时,基于SPEC CPU 2017基准测试的对比显示,Chimera重写后的二进制文件性能,优于现有二进制重写方法,最高性能提升达42.5%。

相关成果论文被计算机系统领域国际顶级会议EuroSys 2026接收。

Chimera概览

© 版权声明

本文由分享者转载或发布,内容仅供学习和交流,版权归原文作者所有。如有侵权,请留言联系更正或删除。

相关文章

暂无评论...